- 您现在的位置:买卖IC网 > Sheet目录364 > SST25VF064C-80-4I-Q2AE-T (Microchip Technology)IC FLASH SER 64M DUAL I/O 8WSON

�� �

�

�

�64� Mbit� SPI� Serial� Dual� I/O� Flash�

�A� Microchip� Technology� Company�

�SST25VF064C�

�Data� Sheet�

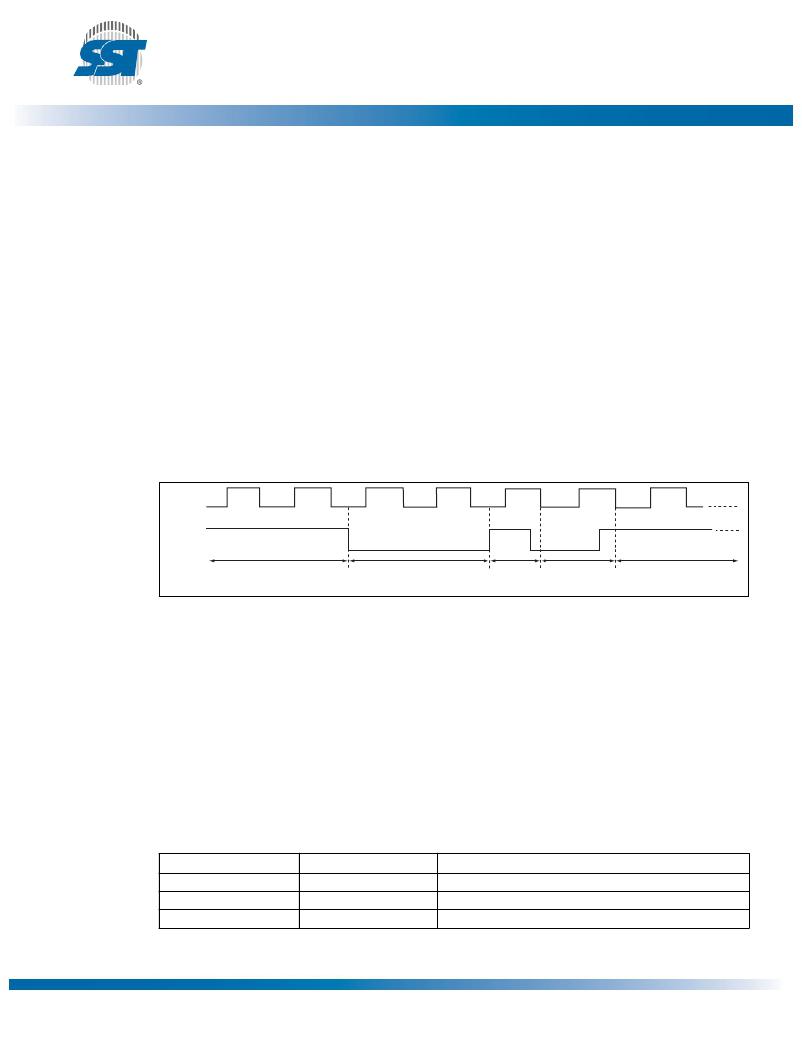

�Hold� Operation�

�The� EHLD� instruction� enables� the� hold� pin� functionality� of� the� RST#/HOLD#� pin.� Once� converted� to� a�

�hold� pin,� the� RST#/HOLD#� pin� functions� as� a� hold� pin� until� the� device� is� powered� off� and� on.� After� the�

�power� cycle,� the� pin� functionality� returns� as� a� reset� pin� (RST#)� after� the� power� on.�

�The� HOLD#� pin� is� used� to� pause� a� serial� sequence� using� the� SPI� flash� memory,� but� without� resetting�

�the� clocking� sequence.� To� activate� the� HOLD#� mode,� CE#� must� be� in� active� low� state.� The� HOLD#�

�mode� begins� when� the� SCK� active� low� state� coincides� with� the� falling� edge� of� the� HOLD#� signal.� The�

�HOLD� mode� ends� when� the� HOLD#� signal’s� rising� edge� coincides� with� the� SCK� active� low� state.�

�If� the� falling� edge� of� the� HOLD#� signal� does� not� coincide� with� the� SCK� active� low� state,� then� the� device�

�enters� Hold� mode� when� the� SCK� next� reaches� the� active� low� state.� Similarly,� if� the� rising� edge� of� the�

�HOLD#� signal� does� not� coincide� with� the� SCK� active� low� state,� then� the� device� exits� from� Hold� mode�

�when� the� SCK� next� reaches� the� active� low� state.� See� Figure� 5� for� Hold� Condition� waveform.�

�Once� the� device� enters� Hold� mode,� SO� will� be� in� high-impedance� state� while� SI� and� SCK� can� be� V� IL� or� V� IH.�

�If� CE#� is� driven� high� during� a� Hold� condition,� the� device� returns� to� Standby� mode.� As� long� as� HOLD#�

�signal� is� low,� the� memory� remains� in� the� Hold� condition.� To� resume� communication� with� the� device,�

�HOLD#� must� be� driven� active� high,� and� CE#� must� be� driven� active� low.� See� Figure� 5� for� Hold� timing.�

�SCK�

�HOLD#�

�Active�

�Hold�

�Active�

�Hold�

�Active�

�1392� F05.0�

�Figure� 5:� Hold� Condition� Waveform�

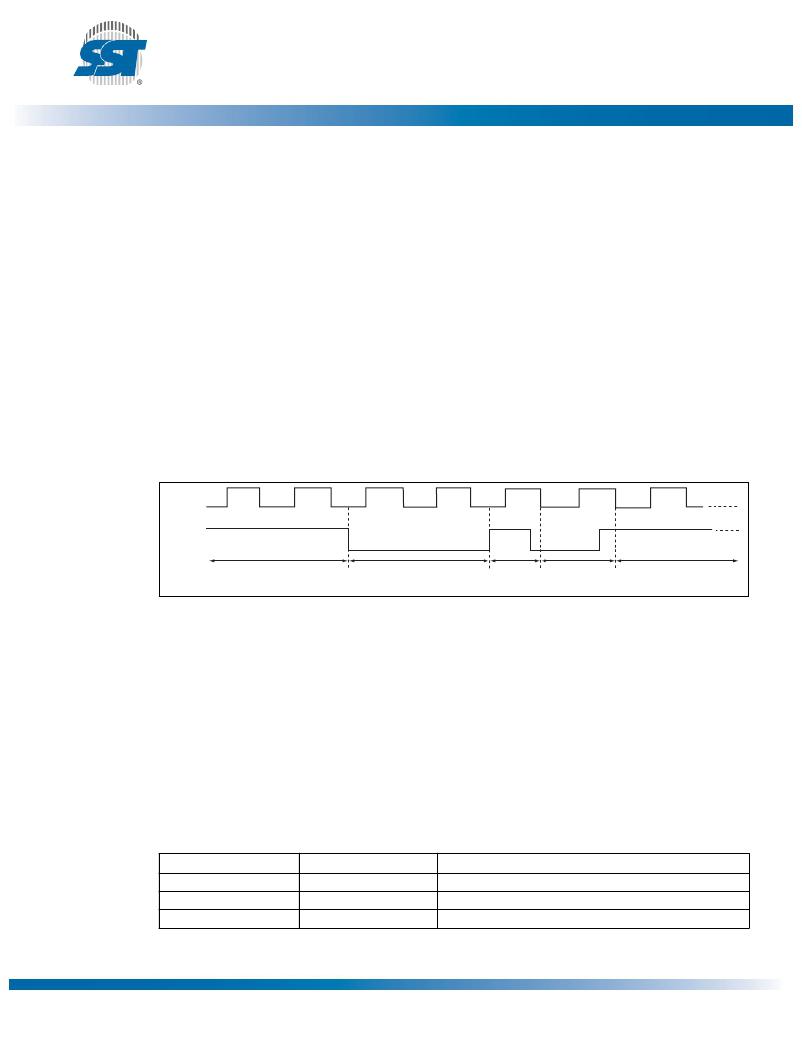

�Write� Protection�

�SST25VF064C� provides� software� Write� protection.� The� Write� Protect� pin� (WP#)� enables� or� disables�

�the� lock-down� function� of� the� status� register.� The� Block-Protection� bits� (BP3,� BP2,� BP1,� BP0,� and� BPL)�

�in� the� status� register� provide� Write� protection� to� the� memory� array� and� the� status� register.� See� Table� 5�

�for� the� Block-Protection� description.�

�Write� Protect� Pin� (WP#)�

�The� Write� Protect� (WP#)� pin� enables� the� lock-down� function� of� the� BPL� bit� (bit� 7)� in� the� status� register.�

�When� WP#� is� driven� low,� the� execution� of� the� Write-Status-Register� (WRSR)� instruction� is� determined� by�

�the� value� of� the� BPL� bit� (see� Table� 3).� When� WP#� is� high,� the� lock-down� function� of� the� BPL� bit� is� disabled.�

�Table� 3:� Conditions� to� execute� Write-Status-Register� (WRSR)� Instruction�

�WP#�

�L�

�L�

�H�

�BPL�

�1�

�0�

�X�

�Execute� WRSR� Instruction�

�Not� Allowed�

�Allowed�

�Allowed�

�T3.0� 25036�

�?2011� Silicon� Storage� Technology,� Inc.�

�7�

�DS25036A�

�06/11�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SST25VF080B-80-4I-QAE-T

IC FLASH SER 8MB 50MHZ SPI 8WSON

SST25VF512-20-4C-SAE-T

IC FLASH SER 512K 20MHZ 8SOIC

SST25VF512A-33-4I-QAE-T

IC FLASH SER 512KB 33MHZ 8WSON

SST25WF040-40-5I-QAE-T

IC FLASH SER 4MB 40MHZ SPI 8WSON

SST25WF080-75-4I-ZAE

IC FLSH SER 8MB 75MHZ SPI 8CSP

SST26VF032A-80-5I-S2AE

IC FLASH 32MBIT 8SOIC

SST38VF6402-90-5I-B3KE-T

IC FLASH MPF 64MBIT 90NS 48TFBGA

SST39LF802C-55-4C-MAQE-T

IC FLASH MPF 8MBIT 48-WFBGA

相关代理商/技术参数

SST25VF064C-80-4I-Q2CE

制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash

SST25VF064C804IS3AE

制造商:Microchip Technology Inc 功能描述:

SST25VF064C-80-4I-S3AE

功能描述:闪存 64M (8Mx8) 80MHz Industrial Temp RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel

SST25VF064C-80-4I-S3AE_

制造商:Microchip Technology Inc 功能描述:

SST25VF064C-80-4I-S3AE-T

功能描述:闪存 2.7V to 3.6V 64Mbit SPI Serial 闪存 RoHS:否 制造商:ON Semiconductor 数据总线宽度:1 bit 存储类型:Flash 存储容量:2 MB 结构:256 K x 8 定时类型: 接口类型:SPI 访问时间: 电源电压-最大:3.6 V 电源电压-最小:2.3 V 最大工作电流:15 mA 工作温度:- 40 C to + 85 C 安装风格:SMD/SMT 封装 / 箱体: 封装:Reel

SST25VF064C-80-4I-S3CE

制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash

SST25VF064C-80-4I-SAE

制造商:SST 制造商全称:Silicon Storage Technology, Inc 功能描述:64 Mbit SPI Serial Dual I/O Flash

SST25VF064C804ISCE

制造商:Microchip Technology Inc 功能描述: